ISSLg - Cours d'électronique

Les bus de données et d'adresses

Navigation> electronique/automatisme/bus/bus

Pour plus de détail, voir Floyd - Systèmes numériques 9ème édition :

p538 : Mémoires

p722 : Interfaçage interne (sur CDROM)

p726 : bus standard (sur CDROM)

Nous verrons en premier lieu ce qu'est un bus.

Ensuite les différents types de circuits pouvant être raccordés à un bus seront étudiés :

Finalement, nous verrons l'architecture en bus : comment ces différents circuits peuvent être câblés à un bus, ainsi que les cycles de commande d'écriture et de lecture pour faire transiter les données.

Les bus

Un

bus est un ensemble de n conducteurs (généralement parallèles),

référencés par rapport à la même masse, permettant de véhiculer un

nombre binaire codé sur n bits. En logique 0/5V, chaque conducteur peut

être soit à 0V (0 logique) par rapport à la masse, soit à 5V (1

logique) par rapport à la masse.

Physiquement un bus peut être :

- un câble à n conducteurs et une tresse de masse

- un

ensembre de n pistes (généralement parallèles) sur un circuit imprimé

(PCB=printed circuit board) par rapport à un plan de masse.

- un ensembre de n pistes (généralement parallèles) à l'intérieur d'un circuit intégré (IC=integrated circuit).

Son symbole est :

où le nombre au-dessus de la ligne représente la largeur du bus, c'est-à-dire le nombre de conducteurs du bus.

NB : les bits ou fils sont numérotés de 0 à n-1.

La

notion de bus est largement utilisée en électronique numérique et est

généralement associée à des micro-contrôleurs (automates) ou encore des

micro-processeurs (ordinateurs).

Dans les architectures à micro-contrôleurs ou micro-processeurs, on utilise généralement 3 bus :

- un bus de données : pour véhiculer les données à traiter (en 8, 16, 32, 64 ou 128bits).

- un bus d'adresse : pour indiquer où lire/placer une donnée (en 16, 20, 32 ou 36bits).

- un bus de commande : pour indiquer quelle est l'action à faire (écriture ou lecture...)

Voir : http://fr.wikipedia.org/wiki/Bus_informatique

Les buffers de lecture 3-états

Si

nous connectons plusieurs sorties de circuits logiques sur un même fil

(ex bit3 du bus de donnée), nous créons un court-circuit entre ces

sorties. Il faut donc des sorties spéciales pour interdire ces

courts-circuits.

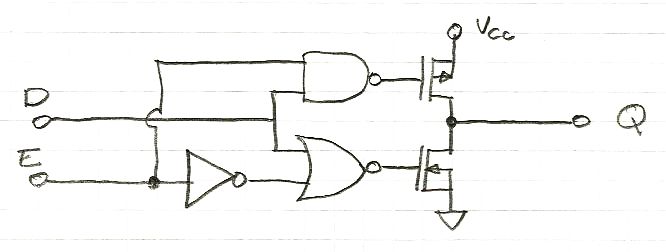

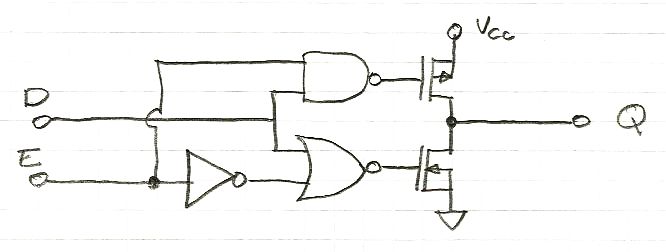

Le 74HC245 possède ce type de sorties :

Les 8 bits de sorties de ce circuit possède un buffer 3 états (3 states output) :

Soit Q = D si E=1

En

effet, si E=0 les deux MOS de sorties sont coupés et la sortie est en

haute impédance, permettant ainsi à un autre circuit de se connecter

sur le bus de données. Cet état en haute impédance est noté "Z" dans la

table de vérité.

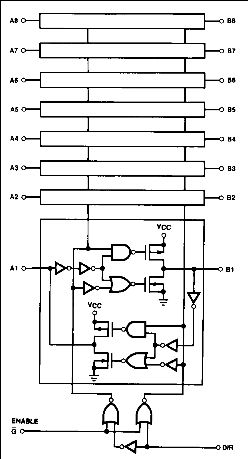

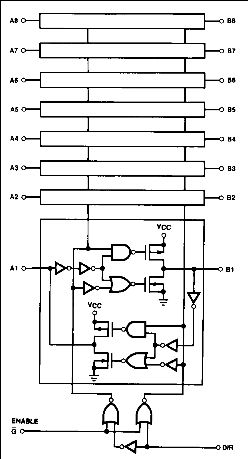

Le 74HC245

est en réalité un peu plus complexe, les 8 bits sont bi-directionnels

grâce à deux buffers 3-états en tête-bêche pour chaque bit. La

direction de transfert se fait avec le bit de commande "DIR".

Notons

également qu'ici que le Enable est inversé : il faut un 0 sur

l'entrée /G pour transférer les bits Ax vers Bx si DIR=1.

Le

74H245 permet donc de câbler plusieurs sorties de 8 bits sur un même

bus de données sans court-circuiter ces sorties. Une seule sortie de 8

bits peut être connectée au bus de donnée à un instant donné en mettant

son /G à 0, tous les autres /G restant à 1 pour empêcher les

courts-circuits.

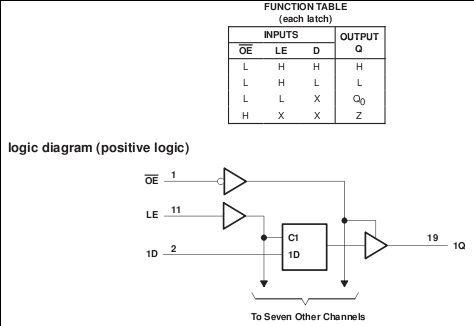

Les registres (latchs) d'écriture

Plusieurs

entrées peuvent être raccordées à un même bus de données, mais il faut

que chaque entrée mémorise sa donnée, vu qu'elle va varier au cours du

temps. Cela peut être réaliser avec des verrous D (D latch).

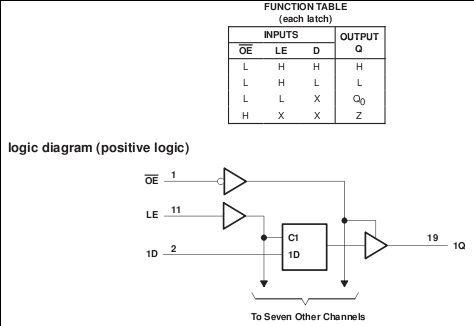

Le 74HC573 permet de mémoriser une entrée de 8 bits.

Les bits Dx sont mémorisés lorsque la commande d'écriture LE est à 1.

Le circuit comporte également des sorties 3 états qui sont actives lorsque /OE est à 0.

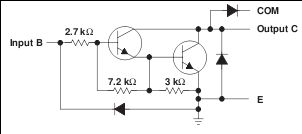

Les

sorties du 74HC573 ne sont pas assez puissantes que pour piloter

directement des relais, des lampes... Aussi ces sorties sont

généralement suivies par des drivers, permettant de booster les sorties

en courant.

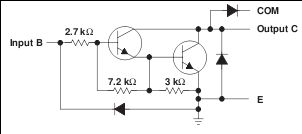

Le driver ULN2803 est constitué de 8 darlingtons (drivers 8 bits) pouvant supporter jusqu'à 500mA.

NB : les diodes servent de protection de l'entrée ou de roue libre pour la sortie en cas de charge "selfique".

Les décodeurs d'adresse

Le décodage d'adresse permet de sélectionner quel buffer est à lire, ou quel registre est à écrire.

Ce

décodage est piloté par un bus d'adresse, indiquant le numéro (en

binaire) du buffer à lire, ou du registre à écrire ; ainsi

que par un bus de commande comportant au minimum deux bits : READ

(lecture) et WRITE (écriture).

Souvent c'est un décodage d'une

plage d'adresses qui est réalisé : une adresse de base suivie de ses n

adresses suivantes (ex pour le port LPT1 : $378 , $379 , $ 37A en

hexadécimal).

Le décodage de l'adresse de base peut se faire sur les MSB d'adresse au moyen d'un comparateur 74hc688 qui compare ces bits de poids forts avec un codage binaire (dip switch ou jumpers) de l'adresse de base.

Les adresses suivantes peuvent ensuite être sélectionnées par un décodeur 74hc154 qui aiguille le READ ou le WRITE sur le bon buffer ou registre.

L'architecture en bus

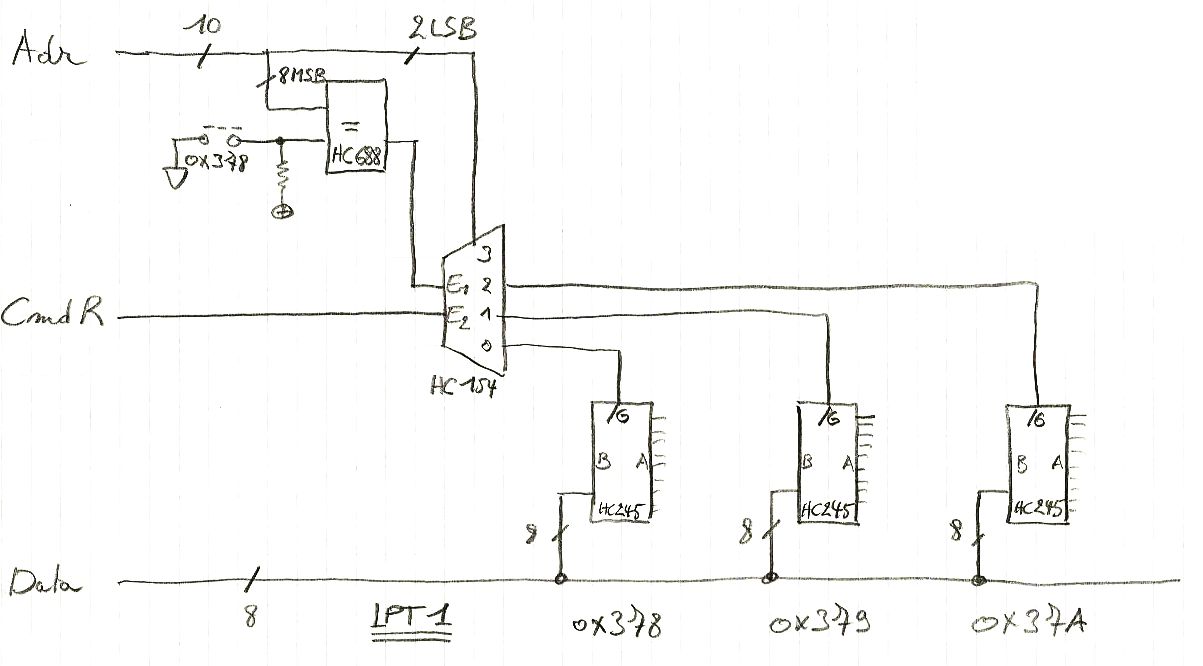

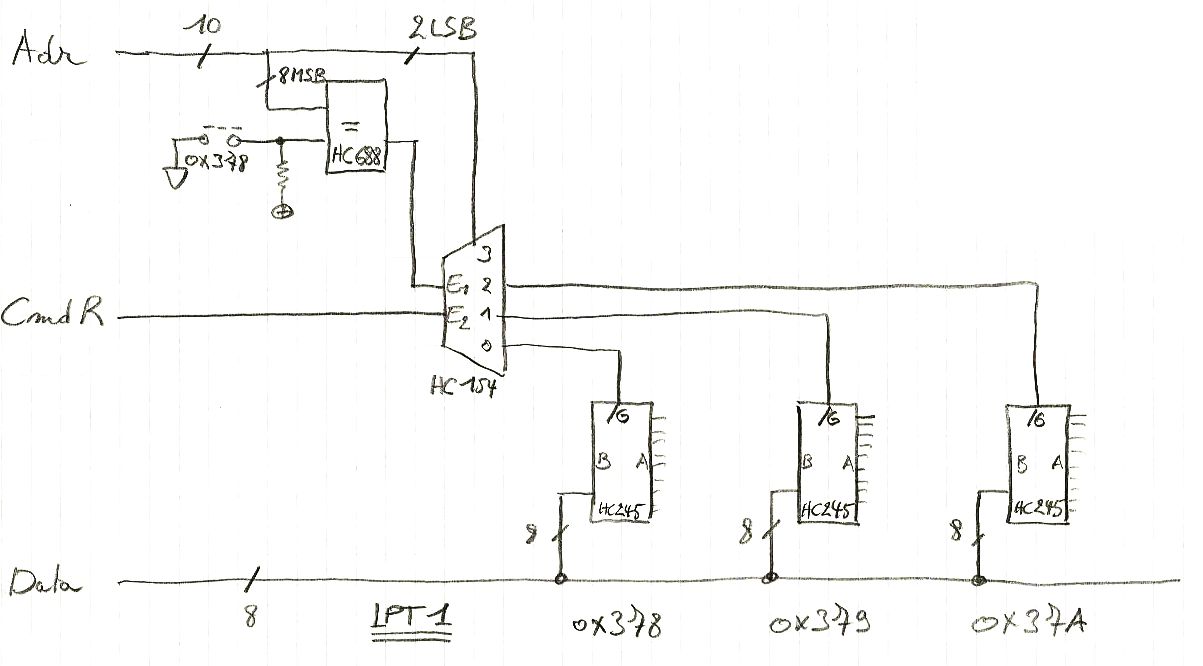

Voici comment ces circuits doivent être raccordés pour une lecture par bus :

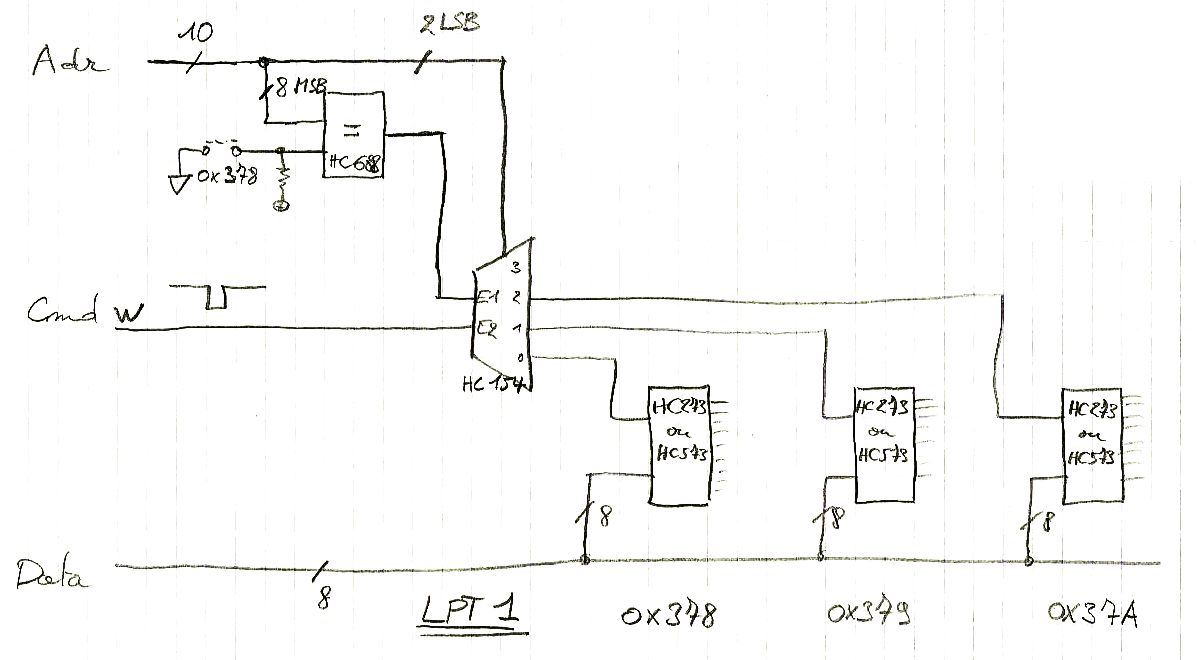

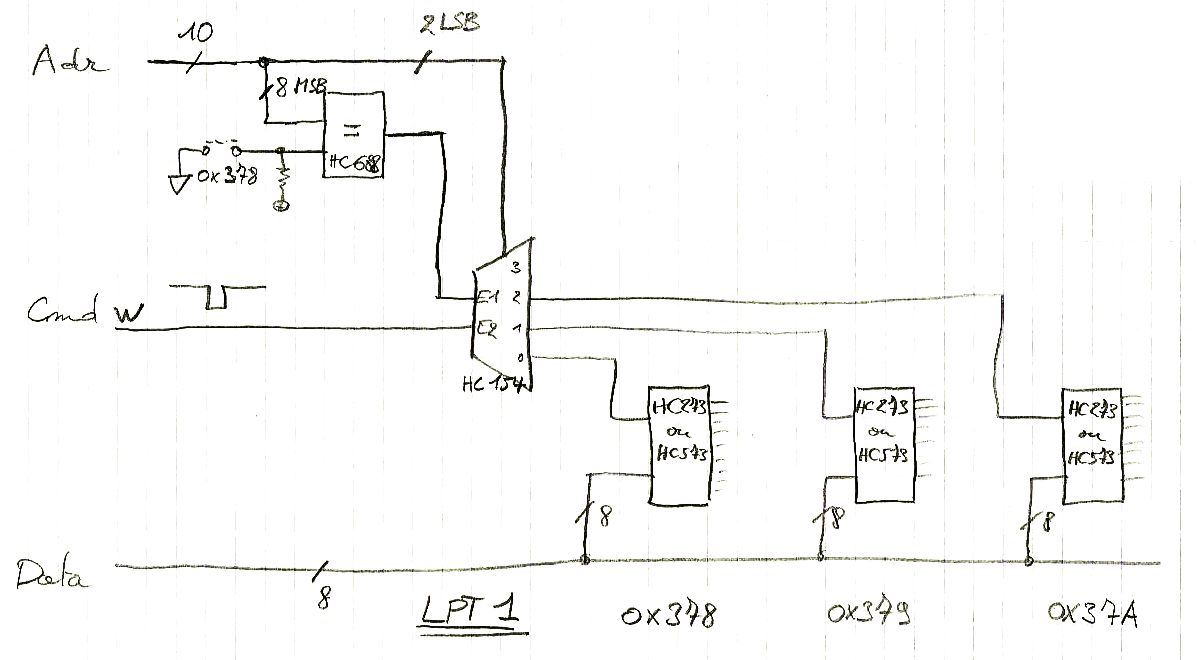

et pour une écriture par bus :

NB

: les sorties du 74HC154 doivent passer par des inverseurs dans le cas

de registres 74HC573 vu que ceux-ci mémorise la donnée lorsque LE est à

1.

Les cycles de lecture et d'écriture

Avec ces circuits,

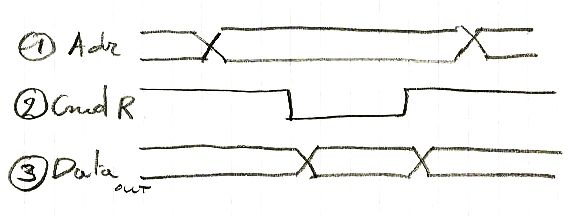

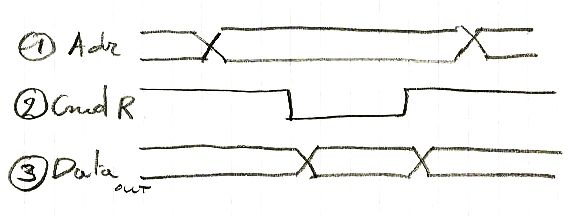

Pour réaliser une lecture, il faut procéder comme suit :

- placer l'adresse sur le bus d'adresses

- faire passer commande /R à 0 pour activer la sortie du 74HC245 sélectionné

- la

donnée à lire apparait sur le bus de données avec un retard de

quelques nsec (le temps d'activation des buffers 3-states du 74HC245)

- remettre la commande /R à 1 une fois que la lecture est faite pour désactiver la sortie du 74HC245.

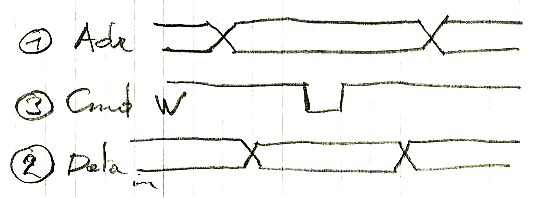

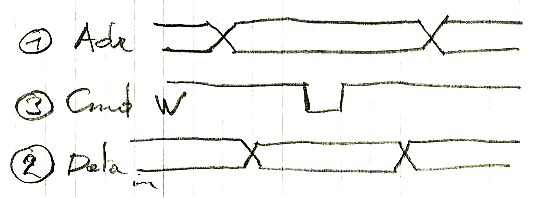

Pour réaliser une écriture, il faut procéder comme suit :

- placer l'adresse sur le bus d'adresses

- placer la donnée sur le bus de données

- faire passer la commande /W à 0 pour activer la mémorisation du 74HC573 sélectionné

- remettre la commande /W à 1 pour remettre le 74HC573 en mode mémoire.

Auteur : Philippot Marc - 19/09/2013