ISSLg

- Cours d'électronique

Comment mémoriser des

états logiques ?

Navigation> electronique/automatisme/portes/bascule

Un relais bistable est déjà à lui seul une mémoire (voir Sorties

électriques simples).

Il est également possible de transformer un relais monostable en relais bistable en mettant un

de ses contacts de sortie en parallèle avec sa commande, de manière à

le maintenir enclenché même si sa commande est ensuite relâchée...

Mais la mémorisation d'états logiques se fait principalement au moyen

de portes logiques, également par rebouclage de sorties sur des entrées.

Les schémas et textes ci-après sont abondament tirés de :

Pour la théorie détaillée, voir : Systèmes numériques - Floyd 9ème édition

p370 : chap 14 - Verrous, bascules et minuteries

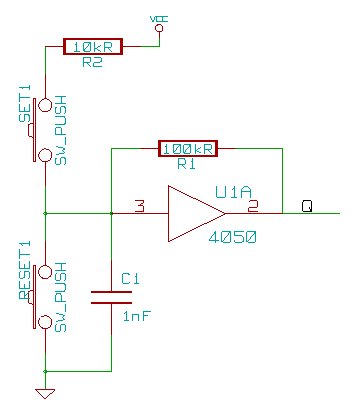

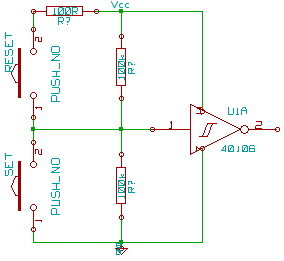

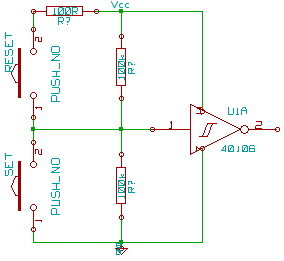

Exemples de mémoires commandées par des contacts

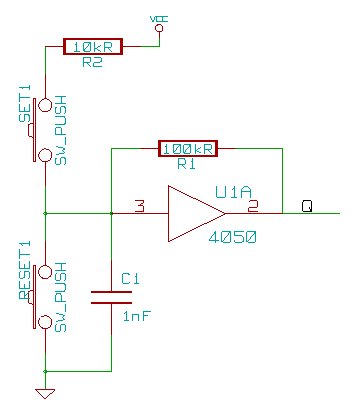

Via le rebouclage de la sortie d'un buffer sur son entrée :

Via le maintien à mi-tension de l'entrée d'un Trigger (ou d'un Timer NE555) :

Mais en électronique, il faut pouvoir commander la mémoire avec des

états logiques et non plus des contacts. C'est ce que font les verrous

ci-dessous.

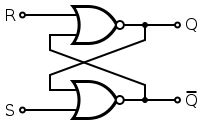

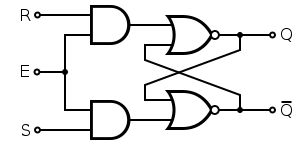

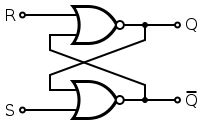

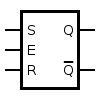

Le verrou RS

Il peut être réalisé par le rebouclage de 2 portes NOR :

Il a deux entrées Set et Reset ; et une sortie Q et son complément

not(Q).

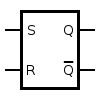

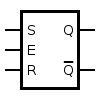

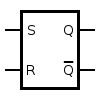

Symbole du verrou RS :

Table de vérité :

| S |

R |

Q |

Q |

remarque |

| 0 |

0 |

q |

q |

mémorisation |

| 0 |

1 |

0 |

1 |

mise à 0 |

| 1 |

0 |

1 |

0 |

mise à 1 |

| 1 |

1 |

0 |

0 |

cas particulier |

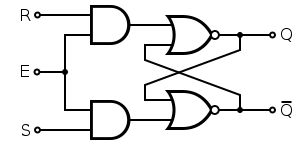

Le verrou RS avec Enable

Le verrou RS ci-dessus peut être complété par l'ajout d'un bit de

commande d'écriture : l'entrée Enable.

Symbole du verrou RS avec E :

Table de vérité :

| E |

S |

R |

Q |

Q |

remarque |

| 0 |

x |

x |

q |

q |

mémorisation |

| 1 |

0 |

0 |

q |

q |

mémorisation |

| 1 |

0 |

1 |

0 |

1 |

mise à 0 |

| 1 |

1 |

0 |

1 |

0 |

mise à 1 |

| 1 |

1 |

1 |

0 |

0 |

cas particulier |

Le Set ou le Reset ne sont possibles que lorsque Enable est à 1.

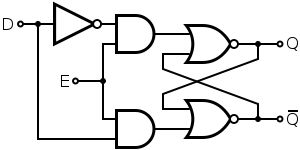

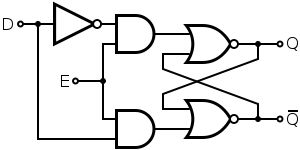

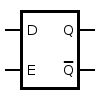

Le verrou D (latch)

Si l'on veut mémoriser un état logique D, il faut dans le schéma

ci-dessus que S=D et R=D ; c'est ce qui est réalisé dans le

circuit suivant :

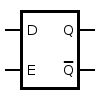

Symbole du verrou D :

Table de vérité :

| E |

D |

Q |

Q |

remarque |

| 0 |

x |

q |

q |

mémorisation |

| 1 |

0 |

0 |

1 |

mise à 0 |

| 1 |

1 |

1 |

0 |

mise à 1 |

L'écriture de D se fait lorsque Enable est à 1 : nous avons enfin une cellule mémoire avec commande d'écriture !

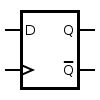

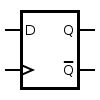

La bascule D (flip-flop)

Elle

est réalisée au moyen de deux verrous D (Master/Slave) piloté par un

signal d'horloge : l'écriture de D se fait à chaque flanc montant de

l'horloge (d'où l'appellation D pour Delay). Cette bascule peut être

utilisée comme registre à décalage pour les conversions de transmission

parallèle/série ; ou encore comme compteur en rebouclant Q sur D.

Symbole de la bascule D :

Table de vérité :

| D |

CLK |

Q |

Q |

remarque |

| d |

|

d |

d |

Q recopie D |

| X |

1,0,front descendant |

q |

q |

mémorisation |

Équation de la bascule : Qn + 1 = D

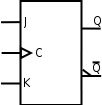

La bascule JK

Il existe également des bascules JK, elles augmentent le comportement

des verrous RS (J=Set & K=Rest) en interprétant la condition R = S

= 1 (J = K = 1) comme une commande de changement d'état de la sortie à

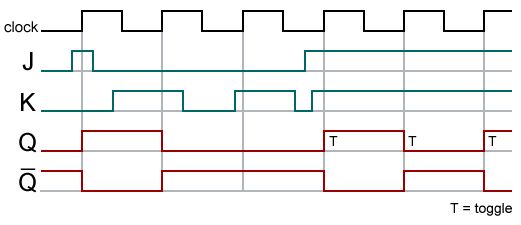

chaques flancs montant du signal d'horloge C : Qn+1 = Qn. Cette particularité est utilisées pour faire des compteurs ou des diviseurs de fréquence.

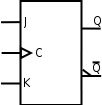

Symbole de la bascule JK :

- Pour J = K = 0, le signal d'horloge est sans effet, il y a conservation du dernier état logique pris par Q et Q : il n'y a jamais de basculement.

- Pour J = K = 1, le système bascule à chaque front d'horloge (montant ou descendant selon les modèles).

- Pour J différent de K, la sortie Q recopie l'entrée J et la sortie Q recopie l'entrée K à chaque front d'horloge.

- On utilise cette bascule pour faire des compteurs. On compte jusqu'à 2n

avec n bascules à la suite et on compte dans l'ordre croissant avec des

bascules à front descendant et dans l'ordre décroissant avec des

bascules à front montant.

Table de vérité :

| J |

K |

Qn+1 |

| 0 |

0 |

Qn |

| 0 |

1 |

0 |

| 1 |

0 |

1 |

| 1 |

1 |

Qn |

Table de vérité alternative:

| Qn |

Qn+1 |

J |

K |

remarque |

| 0 |

0 |

0 |

X |

pour que la sortie reste à 0, il faut que J soit à 0, peu importe K. |

| 0 |

1 |

1 |

X |

pour que la sortie passe de 0 à 1, il faut que J soit à 1, peu importe K. |

| 1 |

0 |

X |

1 |

pour que la

sortie passe de 1 à 0, il faut que K soit à 1, peu importe J. |

| 1 |

1 |

X |

0 |

pour que la sortie reste à 1, il faut que K soit à 0, peu importe J. |

Équation de la bascule :

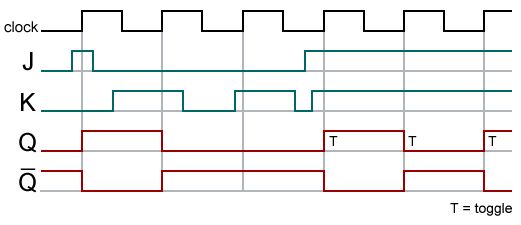

Chronogramme :

Auteur :

Philippot Marc - 26/02/2014